■Programming overview

- Preparing data required for calculation ( LDI / LDY / LDA )

- Description of multiplication-addition expression ( @... )

- Specifying the store destination (> )

Below, we will explain how to code a DSP program in dAsms using a relatively simple example.

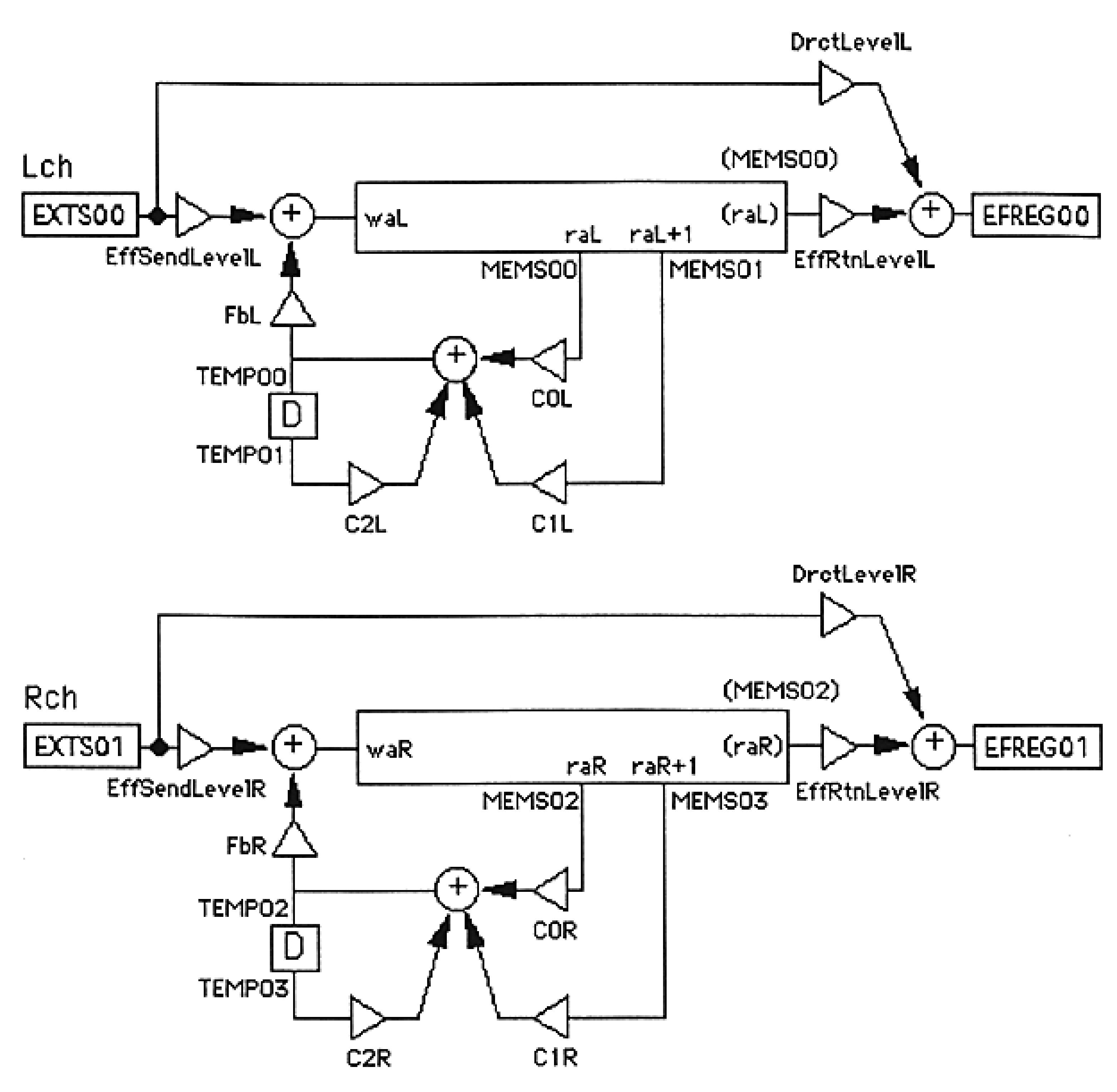

In the example program below, external expansion inputs EXTS00 and EXTS01, which can input CD Audio, etc., are used as Lch and Rch inputs, respectively, and the results of delay (echo) processing performed on Lch and Rch independently are output to EFREG00 and EFREG01, respectively. That is.

■Signal flow diagram

■Coding procedure

1. Definition of coefficient symbol (#COEF)

| Send level to delay | :EffSendLevelL/R |

| Direct signal level | :DrctLevelL/R |

| Return level from delay | :EffRtnLevelL/R |

| Delay signal feedback level | :FbL/R |

-------------------------------------------------- ---

EffSendLevelL=%100

EffSendLevelR=%100

DrctLevelL=%50

DrctLevelR=%50

EffRtnLevelL=%75

EffRtnLevelR=%75

FbL=%50

FbR=%50

-------------------------------------------------- ---

C0L/R

C1L/R

C2L/R

C0L=0.40893

C0R=0.40893

C1L=0.40893

C1R=0.40893

C2L=0.18164

C2R=0.18164

2. Definition of address constant symbol (#ADRS)

waL/R

raL/R

-------------------------------------------------- --------------

waL=ms0.0

raL=ms149.9

waR=ms150.0

raR=ms249.9

-------------------------------------------------- --------------

3.Description of program part (#PROG)

raL

raL+1

MEMS00

MEMS01

LDI MEMS00,MR[raL+DEC]

LDI MEMS01,MR[raL+DEC+1]

- Multiply the value loaded into MEMS00 by the coefficient C0L.

- Multiply the value loaded into MEMS01 by the coefficient C1L and add it to the result of (1).

- Multiply the value of TEMP01 by the coefficient C2L and add it to the result of (2).

- Store the result of (3) in TEMP00.

-------------------------------------------------- ------------------------

@ TEMP01 * C2L + ( MEMS01 * C1L + ( MEMS00 * C0L + ) )> TEMP00

-------------------------------------------------- ------------------------

- The value of input EXTS00 multiplied by the coefficient EffSendLevelL

- The value stored in TEMP00 in 3-2 (4) multiplied by the coefficient FbL

-------------------------------------------------- ------------------------

@TEMP00 * FbL + ( EXTS00 * EffSendLevelL + )> MW[waL+DEC]

-------------------------------------------------- ------------------------- Data read from address raL on the ring buffer multiplied by coefficient EffRtnLevelL

- The value of input EXTS00 multiplied by the coefficient DrctLevelL

-------------------------------------------------- ------------------------

@EXTS00 * DrctLevelL + ( MEMS00 * EffRtnLevelL + )> EFREG00

-------------------------------------------------- ------------------------

-------------------------------------------------- ------------------------

'dAsms sample program.

'Function:L/R independent delay

'CD Lch Direct + Delayed -> EFREG00

'CD Rch Direct + Delayed -> EFREG01

#COEF

'Levels

EffSendLevelL=%100

EffSendLevelR=%100

DrctLevelL=%50

DrctLevelR=%50

EffRtnLevelL=%75

EffRtnLevelR=%75

FbL=%50

FbR=%50

'FilterCoefs

C0L=0.40893

C0R=0.40893

C1L=0.40893

C1R=0.40893

C2L=0.18164

C2R=0.18164

#ADRS

waL=ms0.0

raL=ms149.9

waR=ms150.0

raR=ms249.9

#PROG

'Lch

LDI MEMS00,MR[raL+DEC]

LDI MEMS01,MR[raL+DEC+1]

@ TEMP01 * C2L + ( MEMS01 * C1L + ( MEMS00 * C0L + ) )> TEMP00

@ TEMP00 * FbL + ( EXTS00 * EffSendLevelL + )> MW[waL+DEC]

@EXTS00 * DrctLevelL + ( MEMS00 * EffRtnLevelL + )> EFREG00

'Rch

LDI MEMS02,MR[raR+DEC]

LDI MEMS03,MR[raR+DEC+1]

@ TEMP03 * C2R + ( MEMS03 * C1R + ( MEMS02 * C0R + ) )> TEMP02

@TEMP02 * FbR + ( EXTS01 * EffSendLevelR + )> MW[waR+DEC]

@EXTS01 * DrctLevelR + ( MEMS02 * EffRtnLevelR + )> EFREG01

#END

-------------------------------------------------- ------------------------

★ SOUND Manual ★ SCSP/DSP Assembler User's Manual

★ SOUND Manual ★ SCSP/DSP Assembler User's Manual